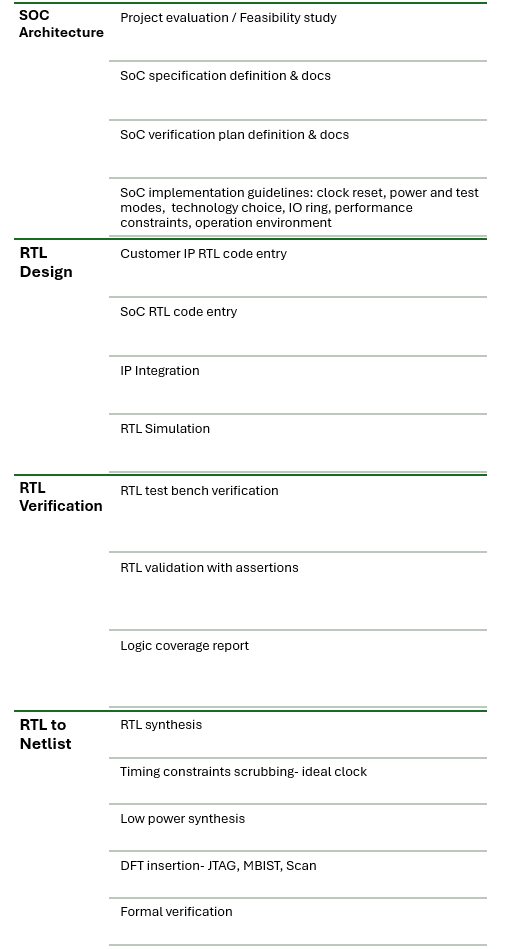

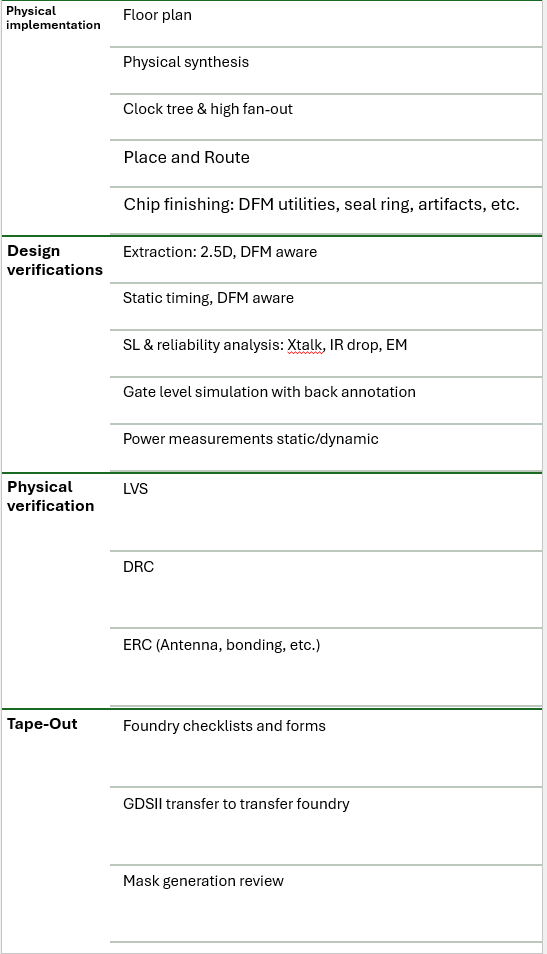

AAS: End to End SoC Design Services

Avnet ASIC Solutions (AAS) delivers a complete spectrum of SoC (System on Chip) design services- From early architecture to tapeout and ramp up to production. Engagements are tailored to your starting point, tool environment, and internal expertise, ensuring seamless integration and a first time silicon outcome.

Flexible Entry Points & Signoff Models

1) System Requirements Handoff

AAS collaborates with your system team to analyze the system requirements creating early specification and architecture requirements.

- Customer provides the system requirements

- AAS will perform a complete spec development

- AAS will build a full architecture solution and the micro-Architecture

- AAS writes the RTL code according to specifications, integrates the required IP and will complete the full RTL to GDSII flow

Best for: Programs that have inhouse system engineering seeking a single ASIC owner.

2) Architecture Specification Handoff

AAS collaborates with your system team to formalize architecture and verification requirements.

- Customer provides Specification and Architecture definition

- AAS builds the micro-Architecture

- AAS writes the RTL code according to specifications, integrates the required IP and will complete the full RTL to GDSII flow

Best for: Programs seeking a single accountable owner for RTL creation, IP integration, and physical implementation, teams that lack internal design capability.

3) RTL Handoff

AAS collaborates with customer to implement their RTL in a Technology specific physical flow.

- Customer will provide a functionally verified synthesizable RTL code of his design and design constraints (performance constraints, IO requirements, supply voltages, technology choice, application environment, etc.)

- AAS performs a complete RTL to GDSII design flow according to the design constraints and will prepare the design or tape-out

Best for: Teams that own RTL but want expert, fixed scope physical implementation, and signoff.

4) Netlist Handoff

AAS collaborates with customer to implement their Netlist in a technology specific physical flow.

- Customer provides a gate level, timing clean netlist with constraints including DFT insertion, ATPG generation and gate level simulations, as well as timing constraints for all DFT modes

- AAS performs a complete RTL to GDSII design flow according to the design constraints and will prepare the design or tape-out

Best for: Customers standardizing internal frontend flows who seek a proven backend partner.

5) GDSII Handoff

AAS collaborates with customer to release his tape-out ready GDSII to the Foundry (FAB) for silicon manufacturing.

- Customer delivers tape-out ready GDSII database

- AAS repeats DRC runs, approve waivers with FAB tapeout your product and manage mask making and silicon manufacturing

- AAS can complement this offering by DFT, package development, test program development and a full production management service

Best for: Teams with a full design capability that would like to have a reliable manufacturing partner that can leverage his cumulative business volume, manufacturing experience and FAB relationship.