Assembly Related Productization Activities

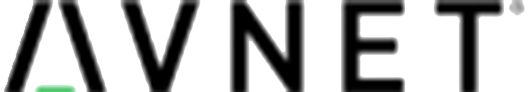

Prior to making a choice of the assembly and test vendor, our engineering and production teams evaluate parameters such as technical and thermal characteristics of the package; existing and forecasted applications of the chip; estimated volumes of the production; vendor's capacity, location and overall profile, and availability for future test platforms.

Once the package type and vendor are selected, we will design the package bonding diagram and substrate according to specification. We will perform the package simulations. Additionally, we will coordinate timely delivery of the tooling, prototype run and a smooth test program transfer to production.

AAS is capable of designing packages of any level of complexity.

- BGA, Flip Chip BGA, LGA, Cu Pillar, WLCSP, QFP, a-QFP, Glass Topped BGA, etc

- AAS has experience in 2.5D packaging, Interposer (CoWos) and SiP design and manufacturing.

- AAS can complement the packaged by dies and passive components provided by Avnet.

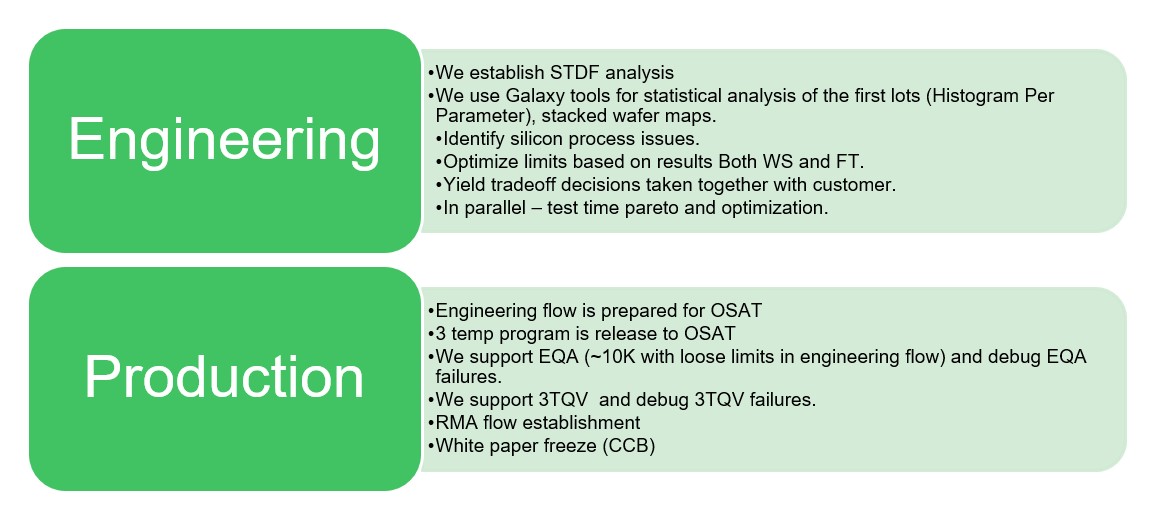

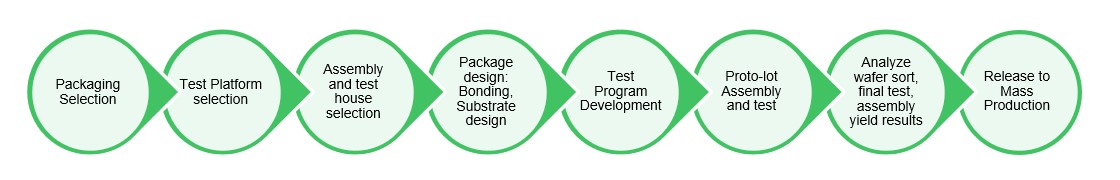

Test Related Productization Activities

Our engineering team has extensive knowledge of all leading test platforms (such as Teradyne, Advantest etc.) and is capable of selecting the best platform to meet the requirements of our customers.

We have an onsite Teradyne and Advantest testers and a 3 temperatures handler, fully compatible to leading OSAT mass production configurations. The testers are used for AAS test programs development and also available for rental.

We also have 3 temp handler, Synax S4, intended to handle small-mid production volumes.

We design the test hardware, such as tester loadboards, sockets, and probe cards for wafer sort. We own the test program generation, debug, and production integration. Our objective is to make sure that the test program is robust enough to detect any possible manufacturing flaws.

AAS's manufacturing team coordinates test program transfer to the selected foundry for the wafer sort and to the chosen assembly and/or test house for the final test. Our ultimate goal is to create a solid, stable and aligned test program at the fab and test house, which will provide high coverage wafer probing and final testing.